Product Summary

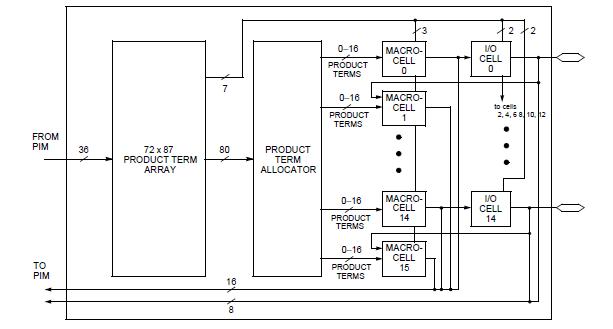

The CY37064P44-125AC is an ISR High-Performance CPLD provides a range of high-density programmable logic solutions with unparalleled system performance. The Ultra37000 family is designed to bring the flexibility, ease of use, and performance of the 22V10 to high-density CPLDs. The architecture is based on a number of logic blocks that are connected by a Programmable Interconnect Matrix (PIM). The CY37064P44-125AC features its own product term array, product term allocator, and 16 macrocells. The PIM distributes signals from the logic block outputs and all input pins to the logic block inputs.

Parametrics

CY37064P44-125AC absolute maximum ratings: (1)Storage Temperature: -65℃ to +150℃; (2)Ambient Temperature with Power Applied: -55℃ to +125℃; (3)Supply Voltage to Ground Potential: -0.5V to +7.0V; (4)DC Voltage Applied to Outputs in High-Z State: -0.5V to +7.0V; (5)DC Input Voltage: -0.5V to +7.0V; (6)DC Program Voltage: -4.5 to 5.5V; (7)Current into Outputs: 16 mA; (8)Static Discharge Voltage: > 2001V (per MIL-STD-883, Method 3015); (9)Latch-up Current: > 200 mA.

Features

CY37064P44-125AC features: (1)In-System Reprogrammable(ISR) CMOS CPLDs, JTAG interface for reconfigurability; Design changes do not cause pinout changes; Design changes do not cause timing changes; (2)High density, 32 to 512 macrocells; 32 to 264 I/O pins; Five dedicated inputs including four clock pins; (3)Simple timing model, No fanout delays; No expander delays; No dedicated vs. I/O pin delays; No additional delay through PIM; No penalty for using full 16 product terms; No delay for steering or sharing product terms; (4)3.3V and 5V versions; (5)PCI-compatible[1]; (6)Programmable bus-hold capabilities on all I/Os; (7)Intelligent product term allocator provides: 0 to 16 product terms to any macrocell; Product term steering on an individual basis; Product term sharing among local macrocells; (8)Flexible clocking, Four synchronous clocks per device; Product term clocking; Clock polarity control per logic block; (9)Consistent package/pinout offering across all densities, Simplifies design migration; Same pinout for 3.3V and 5.0V devices; (10)Packages, 4 to 400 leads in PLCC, CLCC, PQFP, TQFP, CQFP, BGA, and Fine-Pitch BGA packages.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

CY37064P44-125AC |

|

IC CPLD 64 MACROCELL 44LQFP |

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

CY3700i |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CY37032 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CY37032P44-125AC |

|

IC CPLD 32 MACROCELL 44LQFP |

Data Sheet |

Negotiable |

|

||||

|

CY37032P44-125AXC |

Cypress Semiconductor |

CPLD - Complex Programmable Logic Devices 32 Macrocell 5V COM |

Data Sheet |

Negotiable |

|

||||

|

CY37032P44-125AXCT |

Cypress Semiconductor |

CPLD - Complex Programmable Logic Devices 32 Macrocell 5V COM |

Data Sheet |

Negotiable |

|

||||

|

CY37032P44-125JXC |

Cypress Semiconductor |

CPLD - Complex Programmable Logic Devices Ultra37000 32 Macrocell CPLD 5V |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))