Product Summary

The TMS320C6416TGLZ1 is a fixed-point digital signal processor. The TMS320C6416TGLZ1 device is based on the second-generation high-performance, advanced VelociTI very-long-instruction-word (VLIW) architecture (VelociTI.2.) developed by Texas Instruments (TI), making these DSPs an excellent choice for wireless infrastructure applications. The C64x. is a code-compatible member of the C6000. DSP platform. With performance of up to 8000 million instructions per second (MIPS) at a clock rate of 1 GHz, the TMS320C6416TGLZ1 device offers cost-effective solutions to high-performance DSP programming challenges.

Parametrics

TMS320C6416TGLZ1 absolute maximum ratings: (1)Supply voltage ranges: CVDD: -0.5 V to 1.5 V; DVDD: -0.5 V to 4.4 V; (2)Input voltage ranges: (except PCI), VI: -0.5 V to 4.4 V; (3)(PCI), VIP [C6415T and C6416T only]: -0.5 V to DVDD + 0.5 V; (4)Output voltage ranges: (except PCI), VO: -0.5 V to 4.4 V; (5)(PCI), VOP [C6415T and C6416T only]: -0.5 V to DVDD + 0.5 V; (6)Operating case temperature ranges, TC: (default): 0℃ to 90℃; (7)(A version) [A-600, A-720, A.850 only]: -40℃ to 105℃; (8)Storage temperature range, Tstg: -65℃ to 150℃.

Features

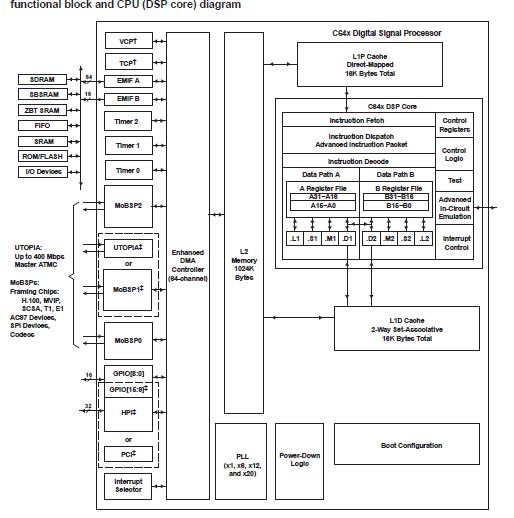

TMS320C6416TGLZ1 features: (1)Highest-Performance Fixed-Point DSPs, 1.67-/1.39-/1.17-/1-ns Instruction Cycle; 600-/720-/850-MHz, 1-GHz Clock Rate; Eight 32-Bit Instructions/Cycle; Twenty-Eight Operations/Cycle; 4800, 5760, 6800, 8000 MIPS; Fully Software-Compatible With C62x; C6414/15/16 Devices Pin-Compatible; Extended Temperature Devices Available; (2)VelociTI.2. Extensions to VelociTI Advanced Very-Long-Instruction-Word (VLIW) TMS320C64x DSP Core; (3)Eight Highly Independent Functional Units With VelociTI.2. Extensions: Six ALUs (32-/40-Bit), Each Supports Single 32-Bit, Dual 16-Bit, or Quad 8-Bit Arithmetic per Clock Cycle; (4)Two Multipliers Support, Four 16 x 16-Bit Multiplies (32-Bit Results) per Clock Cycle or Eight 8 x 8-Bit Multiplies (16-Bit Results) per Clock Cycle; Non-Aligned Load-Store Architecture; 64 32-Bit General-Purpose Registers; Instruction Packing Reduces Code Size; All Instructions Conditional; (5)Instruction Set Features, Byte-Addressable (8-/16-/32-/64-Bit Data); 8-Bit Overflow Protection; Bit-Field Extract, Set, Clear; Normalization, Saturation, Bit-Counting; VelociTI.2. Increased Orthogonality; (6)VCP [C6416T Only], Supports Over 833 7.95-Kbps AMR;Programmable Code Parameters; (7)TCP [C6416T Only], Supports up to 10 2-Mbps or 60 384-Kbps 3GPP (6 Iterations); Programmable Turbo Code and Decoding Parameters; (8)L1/L2 Memory Architecture, 128K-Bit (16K-Byte) L1P Program Cache; (9)(Direct Mapped); 128K-Bit (16K-Byte) L1D Data Cache (2-Way Set-Associative); 8M-Bit (1024K-Byte) L2 Unified Mapped RAM/Cache (Flexible Allocation).

Diagrams

(China (Mainland))

(China (Mainland))