Product Summary

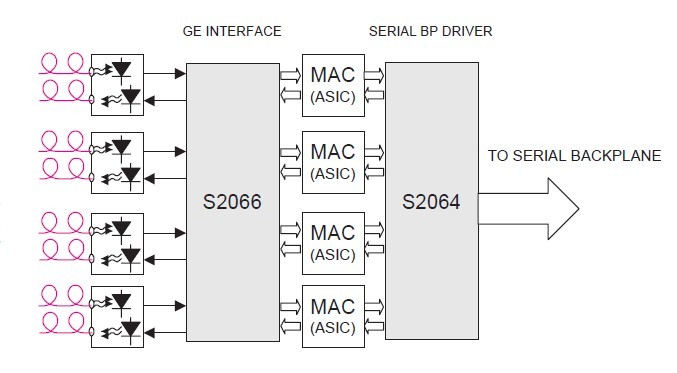

The S2064A is a Communications, Quad Serial Backplane Device. The S2064A facilitates high-speed serial transmission of data in a variety of applications including Gigabit Ethernet, Fibre Channel, serial backplanes, and proprietary point to point links. The chip provides four separate transceivers which can be operated individually or locked together for an aggregate data capacity of >4 Gbps. The applications of the S2064A include Ethernet Backbones, Workstation, Frame buffer, Switched networks, Data broadcast environments, Proprietary extended backplanes.

Parametrics

S2064A absolute maximum ratings: (1)Case Temperature Under Bias: -55 to 125℃; (2)Junction Temperature Under Bias: -55 to 150℃; (3)Storage Temperature: -65 to 150℃; (4)Voltage on VDD with Respect to GND: -0.5 +7.0 V; (5)Voltage on any TTL Input Pin: -0.5 to 3.47 V; (6)Voltage on any PECL Input Pin: 0 VDD V; (7)TTL Output Sink Current: 8 mA; (8)TTL Output Source Current: 8 mA; (9)High Speed PECL Output Source Current: 30 mA; (10)Static Discharge Voltage, TTL I/O: 2000 V; (11)Static Discharge Voltage, PECL I/O: 1500 V.

Features

S2064A features: (1)Broad operating rate range (0.7 - 1.3 GHz), 1062 MHz (Fibre Channel); 1250 MHz (Gigabit Ethernet) line rates; 1/2 Rate Operation; (2)Quad Transmitter with phase-locked loop (PLL) clock synthesis from low speed reference; (3)Quad Receiver PLL provides clock and data recovery; (4)Internally series terminated TTL outputs; (5)On-chip 8B/10B line encoding and decoding for four separate parallel 8-bit channels; (6)32-bit parallel TTL interface; (7)Low-jitter serial PECL interface; (8)Local Loopback; (9)Interfaces with coax, twinax, or fiber optics; (10)Single +3.3V supply, 2.3 W power dissipation; (11)Compact 23mm x 23mm 208 TBGA package.

Diagrams

(China (Mainland))

(China (Mainland))