Product Summary

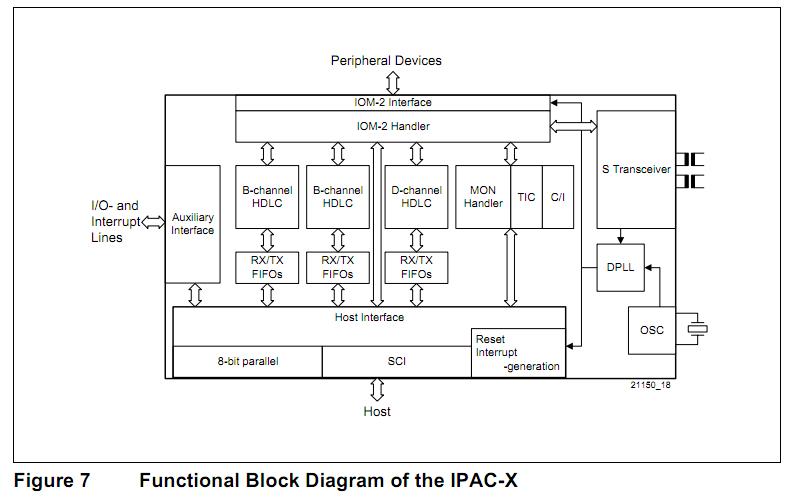

The PSB2115HV1.2 is an ISDN PC Adapter Circuit. It integrates all necessary functions for a host based ISDN access solution on a single chip. The PSB2115HV1.2 is based on the IPAC PSB 2115, combining the functions of ISAC-S PEB 2086 and HSCX-TE PSB 21525, with enhanced features and functionality. It includes the S-transceiver (Layer 1), an HDLC controller for the D-channel and two protocol controllers for each B-channel. The PSB2115HV1.2 can be used for HDLC protocol or transparent access.

Parametrics

PSB2115HV1.2 absolute maximum ratings: (1)Ambient temperature under bias, TA: 0 to 70℃ at PEB; -45 to 85℃ at PEF; (2)Storage temperature, TSTG: –55 to 150℃; (3)Input/output voltage on any pin with respect to ground, VS: –0.3 to 5.25 V; (4)Maximum voltage on any pin with respect to ground, Vmax: 5.5 V.

Features

PSB2115HV1.2 features: (1)Single chip host based ISDN solution; (2)Based on IPAC PSB 2115, integrating ISAC-S and HSCX-TE functionality; (3)8-bit parallel microcontroller interface, Motorola and Siemens/Intel bus type multiplexed or non-multiplexed, direct-/indirect register addressing; (4)Serial control interface (SCI); (5)Microcontroller access to all IOM-2 timeslots; (6)Various types of protocol support (Non-auto mode, transparent mode, extended transparent mode); (7)B-channel HDLC controllers with 128 byte FIFOs; (8)Flexible access to 18-bit timeslots (2B+D) on IOM-2 for IDSL support; (9)D-channel HDLC controller with 64 byte FIFOs; (10)IOM-2 interface in TE, LT-T, LT-S and NT mode, single/double clocks and two strobe signals; (11)D-channel priority handler on IOM-2 for intelligent NT applications; (12)Monitor channel handler (master/slave); (13)IOM-2 MONITOR and C/I-channel protocol to control peripheral devices; (14)Full duplex 2B+D S/T-interface transceiver according to ITU-T I.430; (15)Conversion of the frame structure between the S/T-interface and IOM-2; (16)Receive timing recovery; (17)D-channel access control; (18)Activation and deactivation procedures with automatic activation from power down state; (19)Access to S and Q bits of S/T-interface.

Diagrams

(China (Mainland))

(China (Mainland))